网站备案详细流程徐州seo外包公司

FPGA工作原理、架构及底层资源

文章目录

- FPGA工作原理、架构及底层资源

- 前言

- 一、FPGA工作原理

- 二、FPGA架构及底层资源

-

- 1.FPGA架构

- 2.FPGA底层资源

-

- 2.1可编程输入/输出单元简称(IOB)

- 2.2可配置逻辑块

- 2.3丰富的布线资源

- 2.4数字时钟管理模块(DCM)

- 2.5嵌入式块 RAM(BRAM)

- 2.6底层内嵌功能单元(soft core,软核,区别于软IP核)

- 2.7内嵌专用硬核(hard core,硬核,区别于硬IP核)

- 相关知识快速通道

前言

随着数字电路设计和嵌入式系统应用的不断发展,FPGA(Field-Programmable Gate Array)作为一种灵活、可重构的可编程逻辑器件,受到了越来越广泛的关注和应用。本篇博客将探讨FPGA的原理、架构及底层资源,旨在为读者深入了解FPGA提供全面的专业知识。

一、FPGA工作原理

FPGA的原理基于可编程逻辑块和可编程互连网络。逻辑块是FPGA的基本组成单元,通常由查找表(Look-up Table,LUT)和寄存器组成。查找表是FPGA的关键组件之一,它是一种存储逻辑功能的表格结构,可以实现2输入至6输入的逻辑运算。随着技术的发展和FPGA的进化,FPGA芯片中的逻辑块和查找表的规模不断增加,以满足更复杂的逻辑功能和应用需求。较高输入数量的查找表能够支持更多复杂的逻辑运算,提供更大的灵活性和性能优化。通过编程或配置查找表的值,可以改变逻辑功能的实现。寄存器用于存储状态或临时计算结果,在时钟信号的控制下进行数据的存储和传输。

FPGA的可编程互连网络负责将逻辑块连接在一起以形成所需的电路拓扑。它由全局连线和局部连线两部分组成。全局连线是一组专用的高速互联通道,用于实现逻辑块之间的远距离连接,例如跨时钟域的连接。局部连线则是邻近的逻辑块之间的连线,用于实现邻近互连关系。FPGA的互连网络可通过编程开关(Programmable Switch)的控制以实现连线的通断,使得逻辑块之间的连接变得灵活可变。

深入浅出的理解:如果把FPGA理解为一块电路板,作为设计师就是要去利用这块电路板去通过选用器件和选通布线的方式设计自己要用的电路。这个板子上有很多器件,且各种类器件的位置已经固定,器件之间存在丰富的布线资源,器件和布线都是可以通过编程决定是否选用。设计的过程就是根据功能选用不同的器件,再选通设计中的布线。最后形成目标电路。

二、FPGA架构及底层资源

1.FPGA架构

目前主流的FPGA仍以查找表技术为基础,主要由六部分组成:可编程输入输出单元(IOB)、可编程逻辑单元(CLB)、完整的时钟管理(DCM)、嵌入块状RAM(BRAM)、布线资源、内嵌的底层功能单元(soft core,软核,区别于软IP核)和内嵌专用硬件模块(hard core,硬核,区别于硬IP核)。其中最为主要的是可编程输出输出单元、可编程逻辑单元和布线资源。

IP核一般分为软IP核,硬IP核和固IP核。和上述的软硬核并不是同一个定义范畴。软核(soft core)和硬核(hard core)是FPGA中的两种不同类型的处理器核心或其他复杂的数字逻辑功能的实现方式。

软核(soft core)通常是指通过FPGA中的逻辑资源进行编程实现的处理器核心或其他复杂的数字逻辑功能,它们的实现是通过FPGA内部的逻辑单元和存储单元来完成的。一个常见的软核是Xilinx(现在被AMD收购)的MicroBlaze,它是一款可在Xilinx FPGA中实现的32位RISC处理器核心,设计者可以根据自己的需求对其进行配置和定制,以满足特定的应用需求。另一个常见的软核是Altera(现在被Intel收购)的Nios II,也是一款可在FPGA中实现的可编程处理器核心。

硬核(hard core)则是指在FPGA芯片的物理结构中以硬件形式实现的处理器核心或其他专用的硬件模块。这种硬件功能通常由FPGA芯片的制造厂商直接设计和实现,并在FPGA芯片中进行硬件布局,与FPGA中的逻辑资源分离。举例来说,一些FPGA芯片可能内置了ARM处理器的硬核,这些ARM处理器核心是作为FPGA芯片的一部分直接集成在硅片中,用户可以直接利用这些处理器核心来实现特定的处理器功能,而不需要通过FPGA的逻辑资源来实现。

因此,软核和硬核代表了FPGA中实现处理器核心或其他复杂逻辑功能的两种不同方式,软核通过FPGA中的逻辑资源进行编程实现,而硬核则是直接作为FPGA硅片的一部分实现的,两者各有优劣,选择取决于具体的应用需求和设计考虑。`

2.FPGA底层资源

2.1可编程输入/输出单元简称(IOB)

可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,用于完成不同电气特性下对输入/输出信号的驱动与匹配要求,其示意结构如图1-2所示。FPGA内的I/O按组分类,每组都能够独立地支持不同的 I/O标准。通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上下拉电阻。目前,I/O口的频率越来越高,一些高端的 FPGA通过 DDR寄存器技术可以支持高达多个Gb/s的数据速率。

外部输入信号可以通过IOB模块的存储单元输入到 FPGA的内部也可以直接输入FPGA内部。当外部输入信号经过IOB模块的存储单元输人到FPGA内部时,其保持时间(Hold Time)的要求可以降低,通常默认为0。

为了便于管理和适应多种电气标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压Vcco决定,一个bank 只能有一种 Vcco,但不同 bank的 Vcco可以不同。只有相同电气标准的端口才能连接在一起,Vcco相同是接口标准的基本条件。

关于IOB需要注意:

IOB的结构如上,PAD即与外界连接焊盘引脚,同时有一个IBUF和OBUF。当配置为output时,连接左边的OBUF,配置为input时,连接右边的IBUF。在FPGA中,每一个IOB都有与之对应的一个xIOI3模块(有LIOI3和RIOI3之分,由三个触发器Flip-Flop组成,TFF,OFF和IFF),且其布线资源比较固定,使用xIOI3中的触发器有一个较大的好处,就是其布线资源固定,且最靠近各个引脚,可以实现较低的延迟,在某些特定的场合如高速数据采样下,使用xIOI3可以实现良好的采样效果。如果不使用IOB的触发器而连接普通的Slice内部寄存器,则信号进入第一级寄存器的布线会因为每次综合结果的不同而各有不同,且由于Slice距离接口较远,有可能导致高速信号的采样不正确,不满足时序要求。

一般情况下IOB的寄存器缺省为OFF,如果需要设置接口的寄存器,可以通过下列约束实现:set_property IOB TRUE {get_ports your_port_name}如果需要取消接口的寄存器,可以通过下列约束实现:set_property IOB FALSE {get_ports your_port_name}

2.2可配置逻辑块

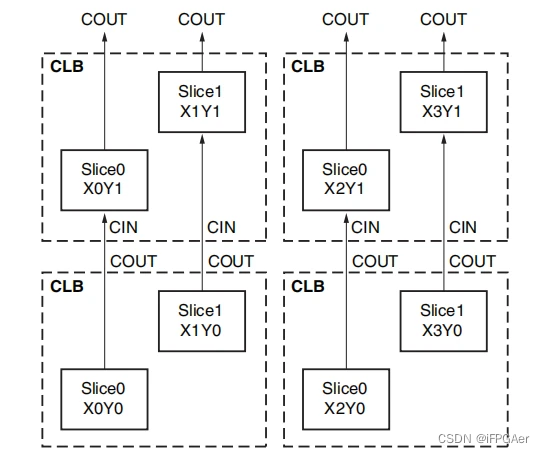

可配置逻辑块CLB(Configure Logic Block)是实现组合逻辑和时序逻辑的主要资源,由一对Slice(片单元)组成,每一个CLB都是连接到了一个交换矩阵(Switch Matrix)中。

每个Slice资源包含4个6输入的LUT,8个FF以及MUX和Carry。Slice又可分为SliceL和SliceM两种类型,在7系列器件中,大约2/3的Slice为SliceL,其余为SliceM,两者区别是SliceM可配置为分布式RAM(Distribute RAM)和移位寄存器,SliceL则不行。

每个CLB都包含一对Slice,这对Slice可能都是SliceL或是一个SliceL和一个SliceM。属于一个CLB中的SliecL和SliceM是独立的,无相互连接的线路,只有属于同一列的Slice之间才会通过进位链进行连接。每个Slice有一个坐标XcYr,r为slice的列序号,c为行序号,同一个CLB的slice行序号是相同的。

2.3丰富的布线资源

FPGA芯片内部有丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类:

1.全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

2.长线资源,用于完成芯片 bank 间的高速信号和第二全局时钟信号的布线;

3.短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

4.分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中,设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。几乎遇不到需要手动去布局布线的情况。

2.4数字时钟管理模块(DCM)

用于生成和管理芯片内部的时钟信号,包括时钟分频、相位锁定和时钟多路复用等功能,确保设计中的时序要求得到满足。目前,业内大多数FPGA均提供数字时钟管理,在内部资源中通常整合为CMT(Clock Manage Tile,时钟管理模块),每个区域对应一个CMT,一个CMT由一个MMCM(Mix-mode Clock Manager)和1个PLL(Phase Locked Loop)组成。主要起到频率综合、去抖动和去偏斜的作用。

对于我们一般设计者来说,最常见的就是用DCM去产生FPGA设计中要用到的时钟。

2.5嵌入式块 RAM(BRAM)

1.架构和特性:

BRAM 是专门为 FPGA 设计而优化的存储资源。它是内置在 FPGA 中的硬件块,能够提供高速、低功耗和可配置的存储功能。

BRAM 通常由多个存储块组成,每个存储块都有一个比特宽度和一个数据深度。每个存储块由一个寄存器数组、读取端口和写入端口组成。

BRAM 可以被配置成单端口 RAM、双端口 RAM、内容寻址存储器(CAM)和 FIFO 等不同的存储结构,以适应各种应用需求。

2.容量和配置:

BRAM 的容量通常以位宽和深度来描述,例如 18Kbit 表示容量为 18 千比特,深度为 1024,常见的容量包括 18Kbit、36Kbit 等,不同型号的 FPGA 器件会提供不同大小和规格的 BRAM。

BRAM 的位宽决定了每个存储位置可以存储的二进制位数,而深度则确定了存储位置的数量。开发者可以根据需要调整 BRAM 的位宽和深度来满足存储需求。

3.用途和应用:

BRAM 在 FPGA 中有广泛的应用场景。它可以用于存储程序指令、缓存数据、实现状态机或 FIFO 缓冲区等。

BRAM 还可用于存储查找表(LUT)和存储器初始化值。对于存储器初始化值,可以在设计中使用 BRAM 以提高初始化数据的可读性和灵活性。

4.优势和注意事项:

BRAM 提供了低延迟和高带宽的存储能力,在许多应用中比分布式 RAM 更适合。

使用 BRAM 可以节省逻辑资源,因为 BRAM 在 FPGA 中是内置的,不占用额外的逻辑单元。

需要注意的是,使用 BRAM 需要合理规划存储容量,并注意时钟和数据控制信号的正确配置,以确保正确的数据存储和访问。

2.6底层内嵌功能单元(soft core,软核,区别于软IP核)

内嵌功能模块主要指 DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU 等软处理核(Embeded Processor)。正是由于集成了丰富的内嵌功能单元,从而使得单片 FPGA 成为系统级的设计工具,具备了软、硬件联合设计的能力,逐步向 SOC 平台过渡。

DLL和 PLL具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和移相等功能。Xilinx 公司生产的芯片上集成了 DLL,Altera 公司的芯片集成了PLL,Lattice 公司的新型芯片上同时集成了 PLL和DLL。PLL 和DLL可以通过IP 核生成的工具方便地进行管理和配置。

2.7内嵌专用硬核(hard core,硬核,区别于硬IP核)

FPGA 中的内嵌专用硬核是指在 FPGA 芯片中内置的、专门设计用来执行特定功能的硬件模块。这些专用硬核旨在提供特定的功能和性能,与可编程逻辑单元(PL)相比,它们通常具有更高的性能、更低的功耗和更低的时延。以下是对 FPGA 中常见的一些内嵌专用硬核的专业详细介绍:

内嵌处理器核(如 ARM Cortex 等):

FPGA 芯片中常常内置有各种处理器核,如 ARM Cortex-A 系列、Cortex-R 系列、Cortex-M 系列等,用于执行通用计算任务、操作系统运行等应用。

这些处理器核与 FPGA 可编程逻辑结合使用,为系统提供了灵活性和性能的双重优势,可以针对特定应用实现定制化的处理器系统。

数字信号处理器(DSP):FPGA 中通常集成了大量的 DSP 切片,用于高性能数字信号处理、滤波、运算等应用。每个 DSP 切片包含多个乘法器和累加器,可以并行地进行复杂的算术运算。DSP 切片在许多信号处理、通信和图像处理应用中发挥重要作用,可以加速各种数学运算和信号处理操作。

存储器控制器:FPGA 中的存储器控制器硬核用于驱动外部存储器接口,如 DDR SDRAM、QDR SRAM 等,以实现高速的数据读写操作。

存储器控制器硬核通常集成了复杂的时序控制逻辑和高速接口,能够与外部存储器设备进行高效的通信。

通信接口硬核(如 PCIe、Ethernet MAC 等):FPGA 中集成了各种通信接口硬核,如 PCIe 控制器、以太网 MAC 控制器等,用于实现与外部设备的高速数据交换和通信。这些通信接口硬核提供了标准化接口和协议实现,能够轻松地与其他设备进行互联和数据传输。例如,为了适用通信总线与接口标准,很多高端的FPGA内部都集成了串并收发器(SERDES),可以达到数十吉比特/秒的收发速度。

总的来说,FPGA 中的内嵌专用硬核提供了各种用途的硬件加速功能,能够为特定的应用场景提供高性能、低功耗和灵活配置的硬件加速解决方案。开发者可以通过合理地使用这些内嵌硬核,实现复杂的功能和系统,并优化系统性能。

行文仓促,如有错误,欢迎指出!

相关知识快速通道

点击下方链接,快速直达下列文章

《FPGA设计相关技能树》

持续更新ing,欢迎大家关注,一起进行技术探讨~