做网站推广弊端怎么做线上推广

一、前言

前一篇文章已经讲述了64B/66B的编码原理,此篇文章来配置一下7系列GT的64B/66B编码。并讲述所对应的例子工程的架构,以及部分代码的含义。

二、IP核配置

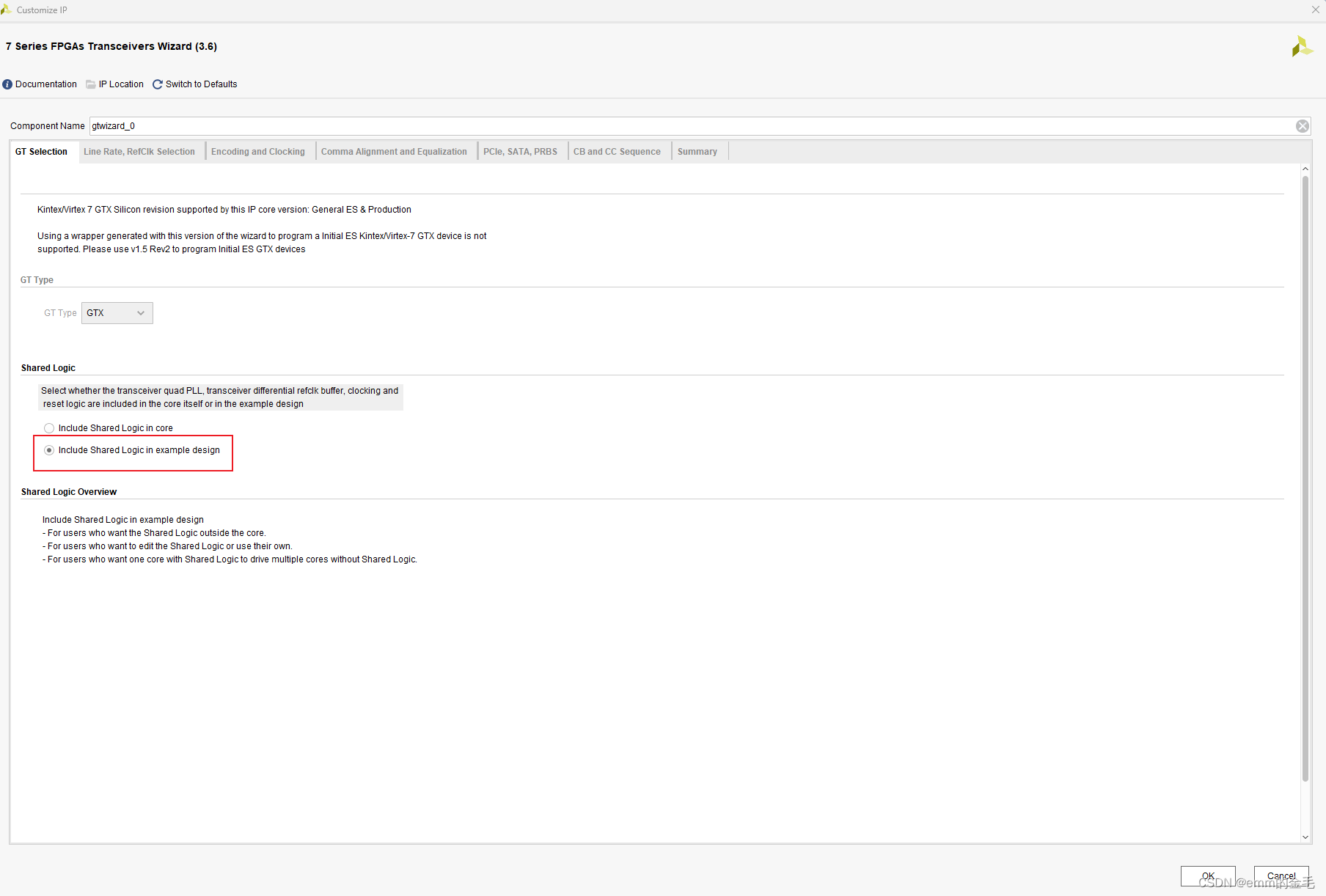

1、打开7 Series FPGAs Transceiver Wizards,选择将共享逻辑放置在example design中

2、线速率、参考时钟选择

2、线速率、参考时钟选择

(1)协议选择从0开始

(2)线速率选择10G,参考时钟选择156.25M

(3)PLL选择:当线速率大于6.6G,自动选择为QPLL

(4)Transceiver选择:保持默认就可以,在布局布线的时候,软件会根据管脚绑定自动选择Transceiver。

3、编码和时钟选择

(1)选择TX、RX外部数据带宽为64bit,选择编码方式为64B/66B with Ext Seq Ctr,内部数据带宽为32bit,DRP时钟为100M

这里的64B/66B with Ext Seq Ctr表示使用64B/66B编码,并使用外部计数器。关于这方面的知识可以去参考UG476中的Gearbox的章节,或者参考此篇文章:详解GearBox设计原理

(2)这里的选项几乎都是有关8B/10B编码的,不需要勾选

(3)这里使用弹性Buffer去做跨时钟域,选择TXUSERCLK的源为TXOUTCLK,TXOUTCLK的源为参考时钟。

(4)这里的选项大多关于PCS、PMA复位或者QPLL、CPLL掉电的,也不需要勾选

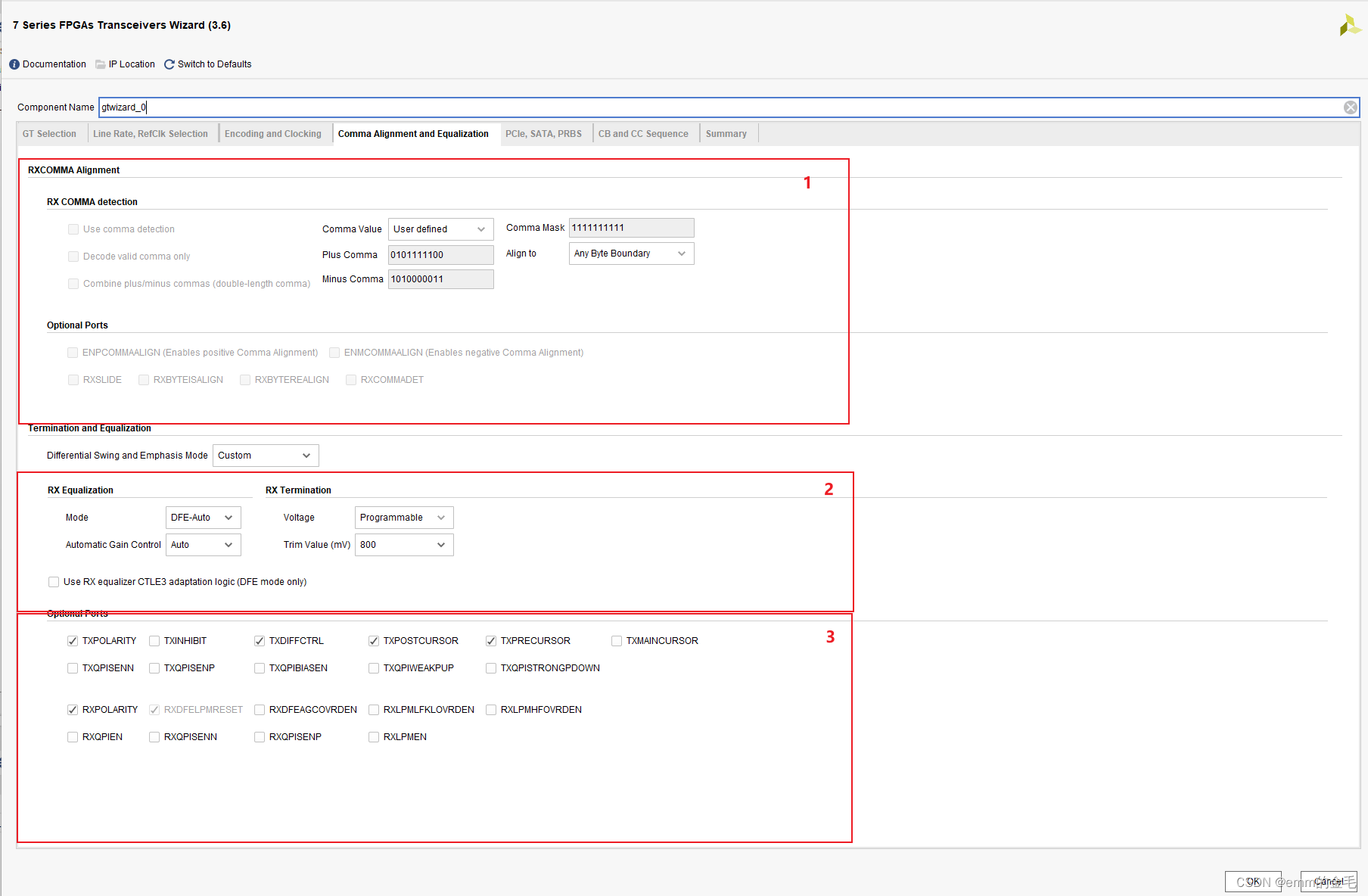

4、逗号对齐和均衡

(1)这里的选项全部都是8B/10B所用到的,所以不能选择

(2)均衡方式这里选择DFE,接收端的阈值电压设置为800mv

(3)这里将TX极性转换、幅值控制、前加重、后加重选上,RX端将RX极性转换选上。

5、这是是使用PCIe或者SATA所用的选项,这里只将loopback勾选

6、通道绑定和时钟矫正

6、通道绑定和时钟矫正

在这里使用序列长度为2的时钟矫正序列,并设置为BC50 7、总结,关注以下内部带宽、外部带宽,参考时钟频率、TXUSERCLK2就好

7、总结,关注以下内部带宽、外部带宽,参考时钟频率、TXUSERCLK2就好

三、例子工程

三、例子工程

工程架构:

Frame_gen模块:用来产生数据帧;

Scrambler模块:用来对所发送的数据进行加扰;

Descrambler模块:用来对接收的模块进行解扰;

Block_syn模块:用于进行块同步。

Frame_chck:用于检测接收到的数据正确性

四、加扰、解扰模块

64B/66B自同步扰码实现随机化,编码所使用的扰码器为: X58+X39+1

扰码的数学原理使用了多项式,多项式的选择通常是基于扰码的特性,包括生成数据的随机度,以及打乱连0和连1的能力。一个简单的扰码器包含一组排列好的触发器,用于移位数据流。大部分的触发器只需要简单地输出下一个比特流即可,但是在复杂的扰码电路中,触发器需要与数据流中的历史比特进行逻辑运算(与和或运算)。

例子工程中加扰、解扰模块是按照如下的示意图进行的:

加扰、解扰程序如下

//加扰模块

module gtwizard_0_SCRAMBLER #

( parameter TX_DATA_WIDTH = 32

)

(// User Interfaceinput wire [(TX_DATA_WIDTH-1):0] UNSCRAMBLED_DATA_IN,input wire DATA_VALID_IN,output reg [(TX_DATA_WIDTH-1):0] SCRAMBLED_DATA_OUT,// System Interfaceinput wire USER_CLK,input wire SYSTEM_RESET

);//***************************Internal Register Declarations******************** integer i;reg [57:0] poly;reg [(TX_DATA_WIDTH-1):0] scrambled_data_i;reg [57:0] scrambler;reg [(TX_DATA_WIDTH-1):0] tempData;reg xorBit;//*********************************Main Body of Code***************************always @(scrambler,UNSCRAMBLED_DATA_IN)beginpoly = scrambler;for (i=0;i<=(TX_DATA_WIDTH-1);i=i+1)beginxorBit = UNSCRAMBLED_DATA_IN[i] ^ poly[38] ^ poly[57];poly = {poly[56:0],xorBit};tempData[i] = xorBit;endend //________________ Scrambled Data assignment to output port _______________ always @(posedge USER_CLK)beginif (SYSTEM_RESET)beginSCRAMBLED_DATA_OUT <= `DLY 'h0;scrambler <= `DLY 58'h155_5555_5555_5555;endelse if (DATA_VALID_IN)beginSCRAMBLED_DATA_OUT <= `DLY tempData;scrambler <= `DLY poly;endendendmodule

//解扰模块

module gtwizard_0_DESCRAMBLER #

( parameter RX_DATA_WIDTH = 32

)

(// User Interfaceinput wire [(RX_DATA_WIDTH-1):0] SCRAMBLED_DATA_IN,input wire DATA_VALID_IN,output reg [(RX_DATA_WIDTH-1):0] UNSCRAMBLED_DATA_OUT,// System Interface

input wire USER_CLK,

input wire SYSTEM_RESET

);//***************************Internal Register Declarations******************** reg [57:0] descrambler;integer i;reg [57:0] poly;reg [(RX_DATA_WIDTH-1):0] tempData;reg [(RX_DATA_WIDTH-1):0] unscrambled_data_i;reg xorBit;//*********************************Main Body of Code***************************always @(descrambler,SCRAMBLED_DATA_IN)beginpoly = descrambler;for (i=0;i<=(RX_DATA_WIDTH-1);i=i+1)beginxorBit = SCRAMBLED_DATA_IN[i] ^ poly[38] ^ poly[57];poly = {poly[56:0],SCRAMBLED_DATA_IN[i]};tempData[i] = xorBit;endend//________________ Scrambled Data assignment to output port _______________ always @(posedge USER_CLK)beginif (SYSTEM_RESET)beginUNSCRAMBLED_DATA_OUT <= `DLY 'h0;descrambler <= `DLY 58'h155_5555_5555_5555;endelse if (DATA_VALID_IN)beginUNSCRAMBLED_DATA_OUT <= `DLY tempData;descrambler <= `DLY poly;endendendmodule

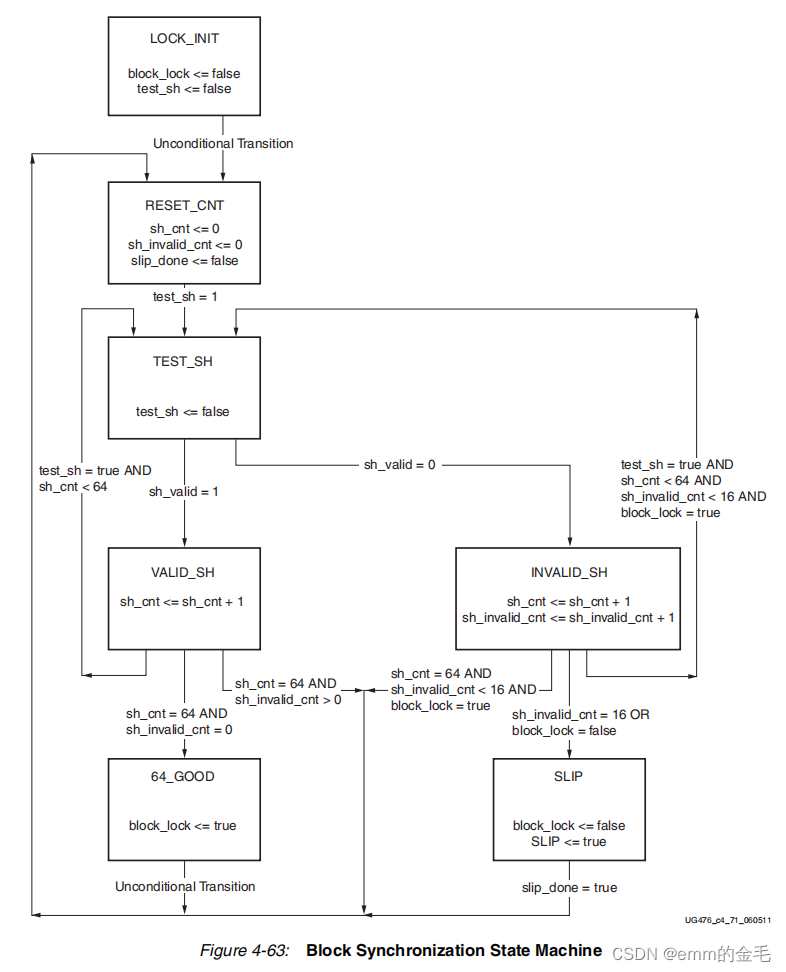

五、块对齐

64B/66B和64B/67B协议依赖于块同步来确定它们的块边界。块同步是必需的,因为在实现块锁定之前,所有传入的数据都未对齐。其目标是通过更改数据对齐方式来搜索有效的同步标头。RXGEARBOXSLIP输入端口用于改变Gearbox数据对齐,以便可以在正常模式下检查所有可能的对齐。RXGEARBOXSLIP输入端口用于改变变速箱数据对齐,以便可以在正常模式下检查所有可能的对齐。这个滑移和测试同步头的过程重复,直到实现块锁定。使用RXGearbox时,FPGA逻辑中需要块同步状态机。

整个过程按照如下的状态机进行:

例子工程的代码如下,将一些关键条件进行注释:

`timescale 1ns / 1ps

`define DLY #1module gtwizard_0_BLOCK_SYNC_SM #

(parameter SH_CNT_MAX = 64,parameter SH_INVALID_CNT_MAX = 16

)

(// User Interfaceoutput reg BLOCKSYNC_OUT,output reg RXGEARBOXSLIP_OUT,input wire [2:0] RXHEADER_IN,input wire RXHEADERVALID_IN,// System Interfaceinput wire USER_CLK,input wire SYSTEM_RESET

);//**************************** Wire Declarations ******************************wire slip_pulse_i; wire next_begin_c;wire next_sh_invalid_c; wire next_sh_valid_c; wire next_slip_c; wire next_sync_done_c; wire next_test_sh_c; wire sh_count_equals_max_i; wire sh_invalid_cnt_equals_max_i; wire sh_invalid_cnt_equals_zero_i; wire slip_done_i; wire sync_found_i; //***************************External Register Declarations*************************** reg begin_r;reg sh_invalid_r; reg sh_valid_r; reg [31:0] slip_count_i; reg slip_r; reg sync_done_r; reg [9:0] sync_header_count_i; reg [9:0] sync_header_invalid_count_i; reg test_sh_r; //**************************** Main Body of Code *******************************// assign sync_found_i = (RXHEADER_IN[1:0] == 2'b01) || (RXHEADER_IN[1:0] == 2'b10);//寻找到数据头//________________________________ State machine __________________________ // State registersalways @(posedge USER_CLK)if(SYSTEM_RESET){begin_r,test_sh_r,sh_valid_r,sh_invalid_r,slip_r,sync_done_r} <= `DLY 6'b100000;elsebeginbegin_r <= `DLY next_begin_c;test_sh_r <= `DLY next_test_sh_c;sh_valid_r <= `DLY next_sh_valid_c;sh_invalid_r <= `DLY next_sh_invalid_c;slip_r <= `DLY next_slip_c;sync_done_r <= `DLY next_sync_done_c;end// Next state logic//begin信号相当于一个复位信号,当同步 或者 滑动计数器已满 或者 同步计数器已经达到最大值但是无效同步计数器有值 或者 同步头无效,同步头的数量到达最大值 都要将计数器清0assign next_begin_c = sync_done_r //已经同步| (slip_r && slip_done_i) //slip的滑动计数器已满| (sh_valid_r && sh_count_equals_max_i && !sh_invalid_cnt_equals_max_i) //同步头有效,同步头的数量到达最大值,无效同步头的数量也没有达到最大值| (sh_invalid_r && sh_count_equals_max_i && !sh_invalid_cnt_equals_max_i && BLOCKSYNC_OUT); //同步头无效,同步头的数量到达最大值,无效同步头的数量也没有达到最大值 快同步继续进行assign next_test_sh_c = begin_r //开始| (test_sh_r && !RXHEADERVALID_IN) //正在检测同步头,并且没有有效的同步头输入,则下一个时钟周期继续检测头部| (sh_valid_r && !sh_count_equals_max_i) //同步头有效,但是有效同步头的数量没有达到最大值| (sh_invalid_r && !sh_count_equals_max_i && !sh_invalid_cnt_equals_max_i && BLOCKSYNC_OUT); //同步头无效、同步头的数量没有到达最大值、无效同步头的数量也没有达到最大值、快同步继续进行assign next_sh_valid_c = (test_sh_r && RXHEADERVALID_IN && sync_found_i); //同步头已经找到,并且输入头有效,并且正在处于查找输入头的状态assign next_sh_invalid_c = (test_sh_r && RXHEADERVALID_IN && !sync_found_i); //正在处于查找输入头的状态,输入头有效,但是同步头没有找到,assign next_slip_c = (sh_invalid_r && (sh_invalid_cnt_equals_max_i || !BLOCKSYNC_OUT)) //下一次滑动的条件:同步头无效,无效同步头计数达到最大值 或者 块同步输出为0| (sh_valid_r && sh_count_equals_max_i && ! sh_invalid_cnt_equals_zero_i && (sh_invalid_cnt_equals_max_i || !BLOCKSYNC_OUT)) //同步头有效并且有效同步头计数器已达到最大值,但是无效同步计数器不为0,并且此时的无效同步计数器达到最大值或者块同步没有输出| (slip_r && !slip_done_i); //滑动信号有效并且滑动计数器没有计满assign next_sync_done_c = (sh_valid_r && sh_count_equals_max_i && sh_invalid_cnt_equals_zero_i); //同步标志:输入的同步头有效并且有效同步头计数器达到最大值并且无效同步器计数为0//________________ Counter keep track of sync headers counted _____________ always @(posedge USER_CLK)if(begin_r) beginsync_header_count_i <= `DLY 10'd0;endelse if (sh_valid_r || sh_invalid_r) //同步计数器在有效同步头和无效同步头的时候都会加1beginsync_header_count_i <= `DLY sync_header_count_i + 10'd1;endassign sh_count_equals_max_i = (sync_header_count_i==SH_CNT_MAX);//________________ Counter keep track of invalid sync headers ____________ always @(posedge USER_CLK)if(begin_r) beginsync_header_invalid_count_i <= `DLY 10'd0;endelse if (sh_invalid_r) //记录无效同步头的数量beginsync_header_invalid_count_i <= `DLY sync_header_invalid_count_i + 10'd1;end// signal to indicate max number of invalid sync headers has been reachedassign sh_invalid_cnt_equals_max_i = (sync_header_invalid_count_i==SH_INVALID_CNT_MAX);// signal to indicate no invalid sync headersassign sh_invalid_cnt_equals_zero_i = (sync_header_invalid_count_i==0);//_______ Counter wait for 16 cycles to ensure that slip is complete _______ assign slip_pulse_i = next_slip_c && !slip_r; //滑动信号输出always @(posedge USER_CLK)RXGEARBOXSLIP_OUT <= slip_pulse_i;//_____________ Ouput assignment to indicate block sync complete _________ always @(posedge USER_CLK)if(!slip_r) slip_count_i <= `DLY 32'h00000000;else slip_count_i <= `DLY {slip_count_i[30:0],RXGEARBOXSLIP_OUT}; //滑动计数器assign slip_done_i = slip_count_i[31];//_____________ Pulse GEARBOXSLIP port to slip the data by 1 bit _________ always @(posedge USER_CLK)if(SYSTEM_RESET || slip_r) BLOCKSYNC_OUT <= `DLY 1'b0;else if (sync_done_r) BLOCKSYNC_OUT <= `DLY 1'b1; //当同步时,证明块同步已完成endmodule六、总结

具体的块对齐过程可以结合仿真看一下,由于过程比较复杂,这里就不细说了