链天网站建设网站seo重庆

FPGA的 MicroBlaze 的 介绍与使用

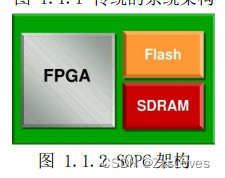

可编程片上系统(SOPC)的设计

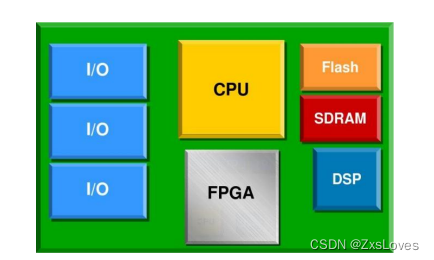

在进行系统设计时,倘若系统非常复杂,采用传统 FPGA 单独用 Verilog/VHDL 语言进行开发的方式,工作量无疑是巨大的,这时调用 MicroBlaze 软核嵌入式处理器 IP 核,将会大大减少开发人员的工作量,从而对于提升工作效率,节约项目成本具有重大意义。采用 FPGA 和 MicroBlaze 进行嵌入式系统设计,可实现多片专用芯片的功能,有利于系统实现小型化、集成化。由于使用 MicroBlaze 软核进行系统搭建时需要利用 FPGA 内部通用资源和相关 IP 核,会占用一定的资源,因此当所要实现的功能较为简单时,则没有必要使用 Microblaze 来实现,传统的 FPGA 设计更具有优势;而当实现的功能较为复杂时(如 GUI 界面的实现),则使用 Microblaze 更具有优势,可以大大提升工作效率。

使用 MicroBlaze 的设计流程

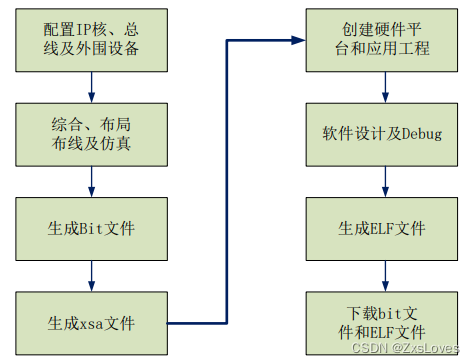

使用 MicroBlaze 进行嵌入式设计包括两部分,分别是硬件设计和软件设计。硬件设计使用到的工具是Xilinx 提供的 Vivado 套件,软件设计使用 Xilix 提供的 Vitis 统一软件平台。在 Vivado 中我们可以在 Block Design 中搭建 MicroBlaze 处理系统,然后生成包含硬件信息的 xsa(Xilinx Shell Archive)文件。利用 xsa 文件在 Vitis 软件中搭建硬件平台,进行软件设计和调试。

第一步:配置 MicroBlaze 核、其他需要的 IP 核以及外围设备。

第二步:硬件设计执行综合、布局布线等。

第三步:生成 BIT 流文件。

第四步:导出包含硬件信息的 xsa 文件。

第五步:启动 Vitis,创建硬件平台工程和应用工程。

第六步:设计软件并调试。

第七步:编译工程生成 ELF 文件。

第八步:将 bit 和 ELF 文件合并为 download.bit 文件并固化。

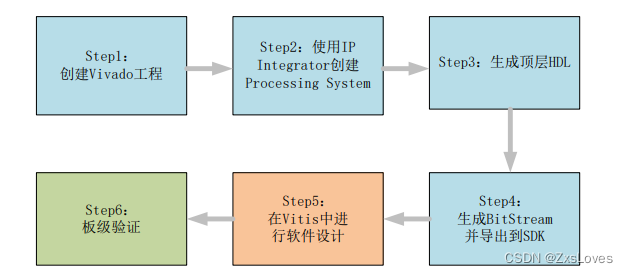

MicroBlaze 软核的嵌入式开发流程

如上图所示,开发流程大体可以分为 6 步。其中 step1 至 step4 为硬件设计部分,在 Vivado 软件中实现;step5 为软件设计部分,在 Vitis 软件中实现;step6 为功能的验证。复杂的程序还涉及 Debug,这个也是在Vitis 软件中实施,具体每一步的操作我们会在后面详细介绍。在简单了解嵌入式系统的开发流程后,接下来我们来看一下什么是嵌入式最小系统。嵌入式最小系统的概念包括以下两个方面:一、它是使系统正常工作的最小条件;二、它是其他系统建立的基础。

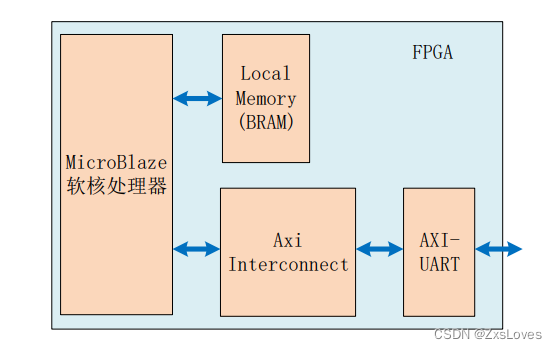

以 MicroBlaze 为核心、LocalMemory(片上存储)为内存,加上传输信息使用的 UART串口就构成了嵌入式最小系统。

当程序比较简单时,Local Memory 可以作为程序的运行空间以及存储空间,空间大小可以根据需要设置最小 8KB 到最大 128KB;当程序比较复杂的时候,我们也可以使用片上搭载的外部存储器(如 DDR3)作为程序的运行空间以及存储空间。

AXI Interconnect IP 核用于将一个(或多个)AXI 存储器映射的主器件与一个(或多个)存储器映射互联。在这里我们解释一下这个术语——互联(Interconnect):互联实际上是一个开关,它管理并指挥所连接的 AXI 接口之间的通信。

实验任务

本章的实验任务是在达芬奇 Pro 开发板上搭建基于 BRAM 的 MicroBlaze 嵌入式最小系统,并使用串口打印“Hello World”信息。

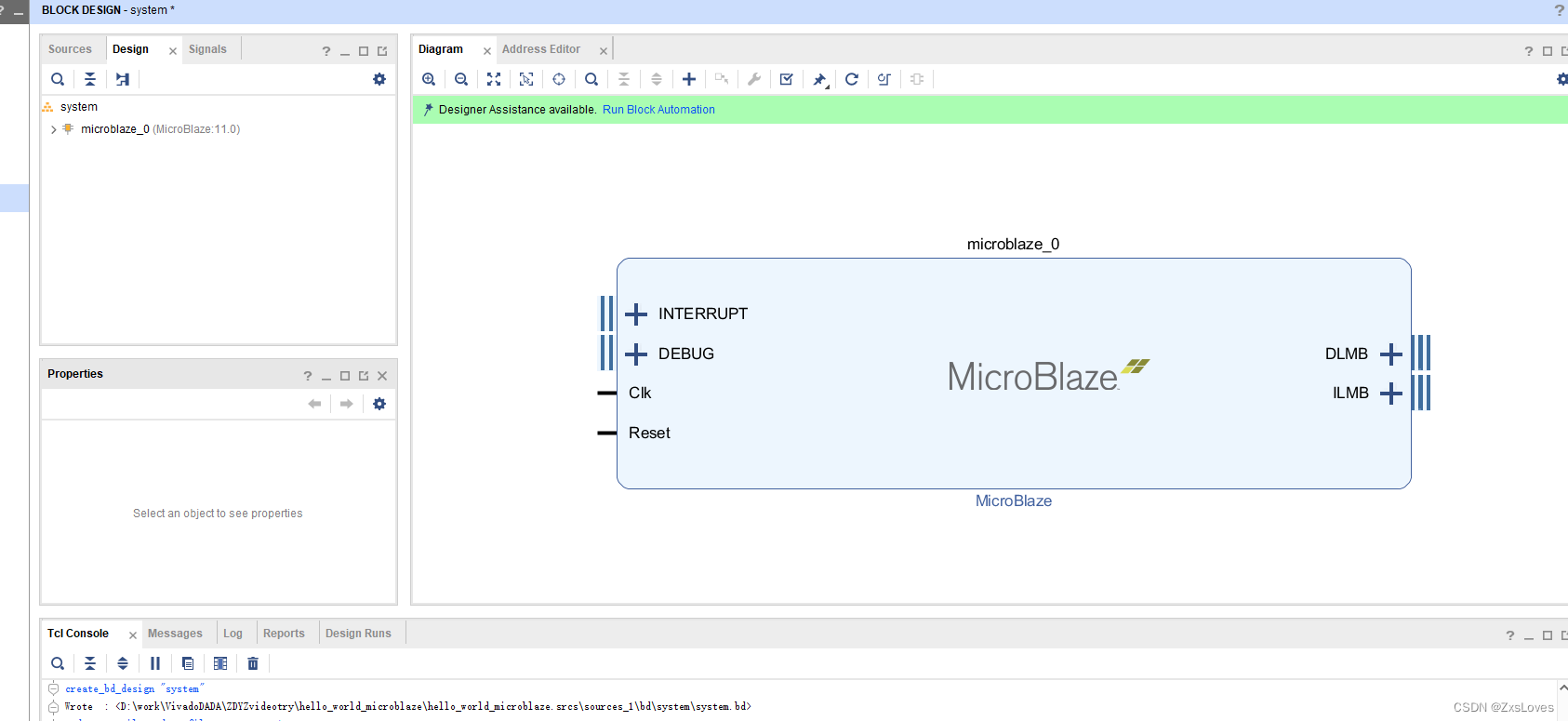

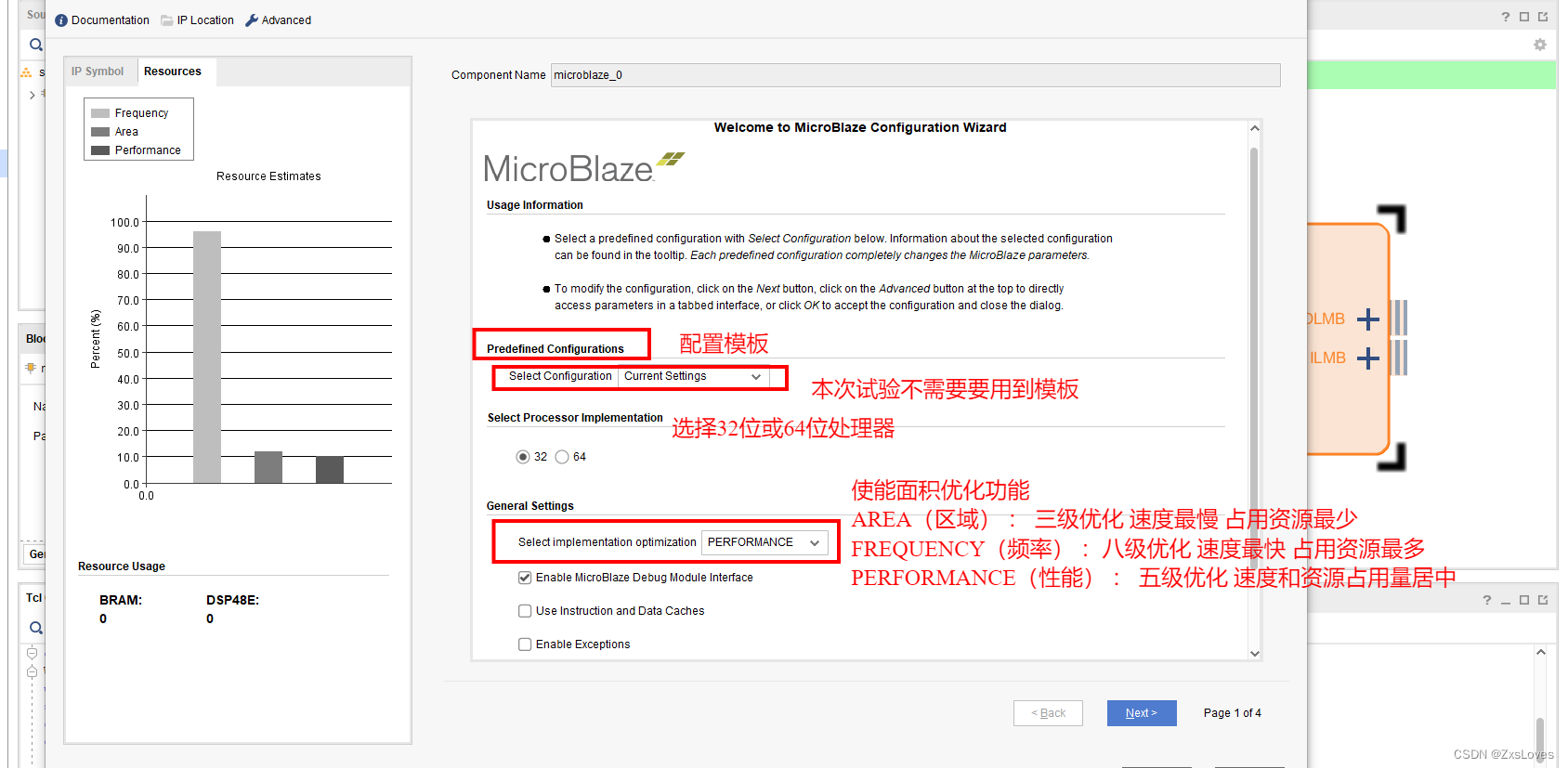

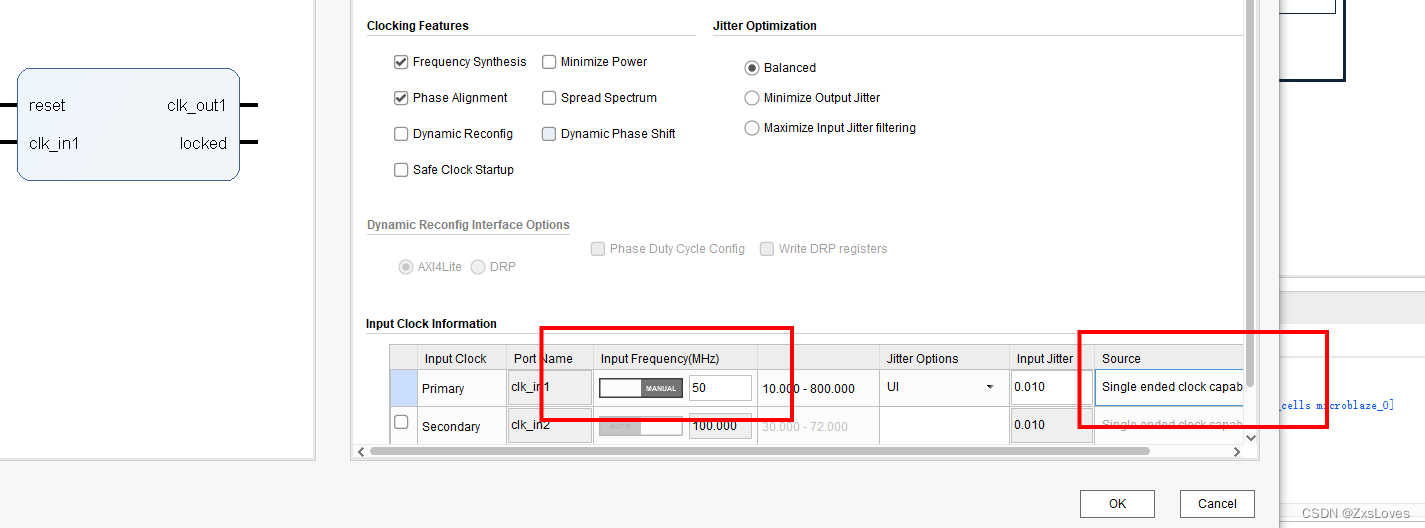

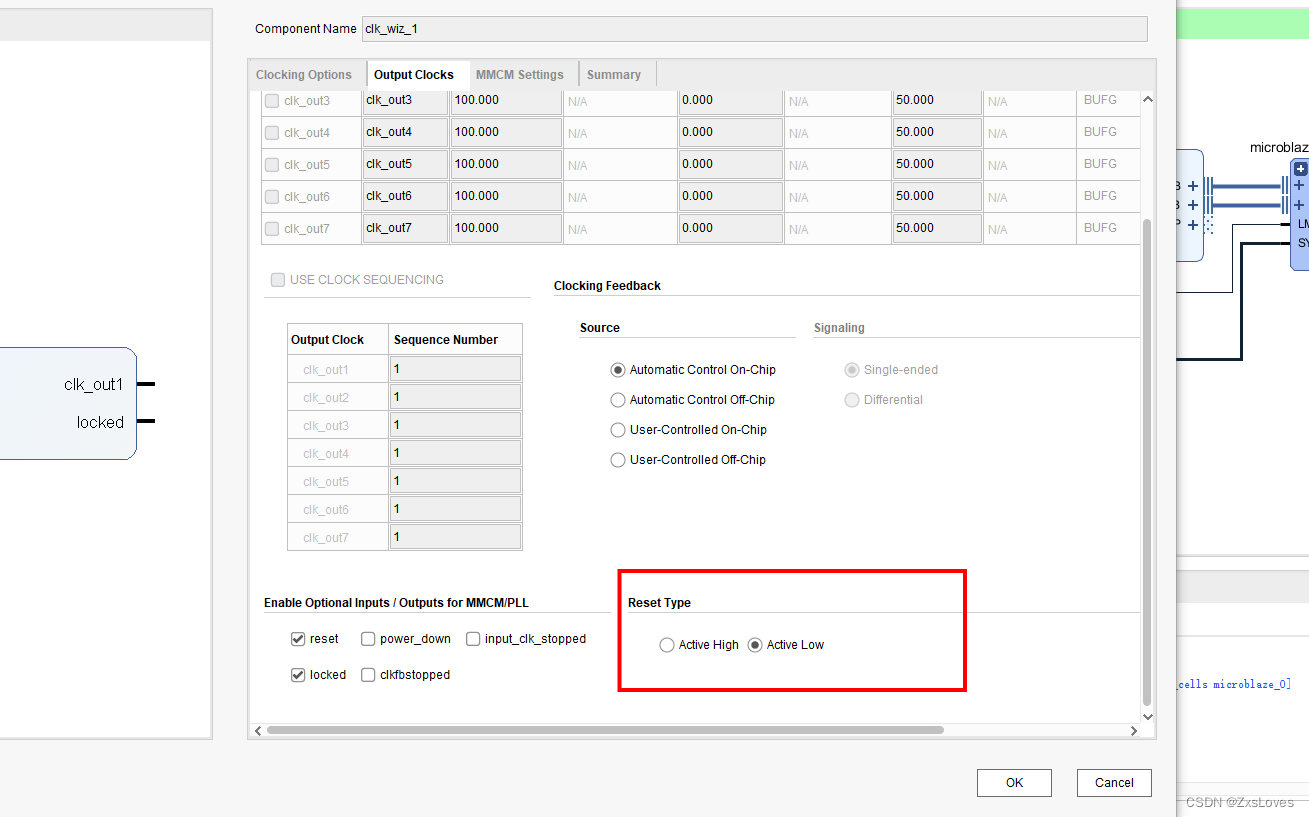

创建MicroBlaze IP核

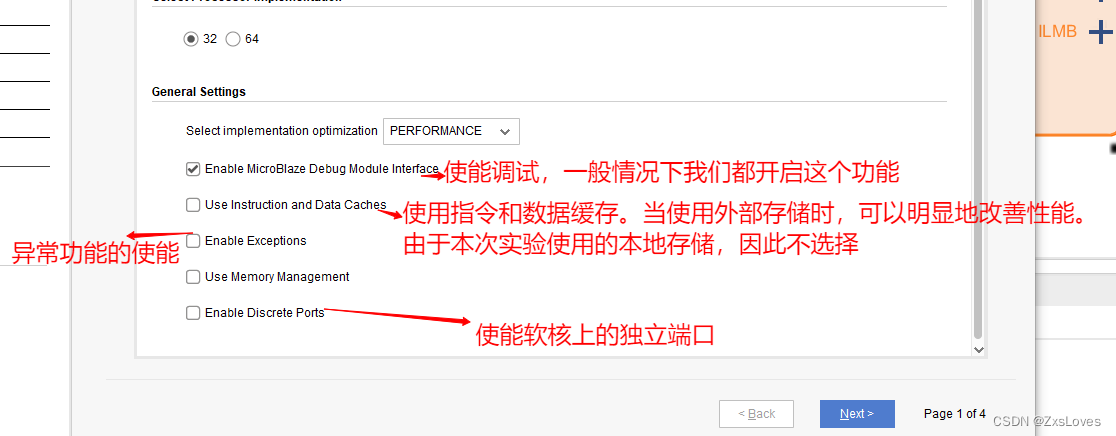

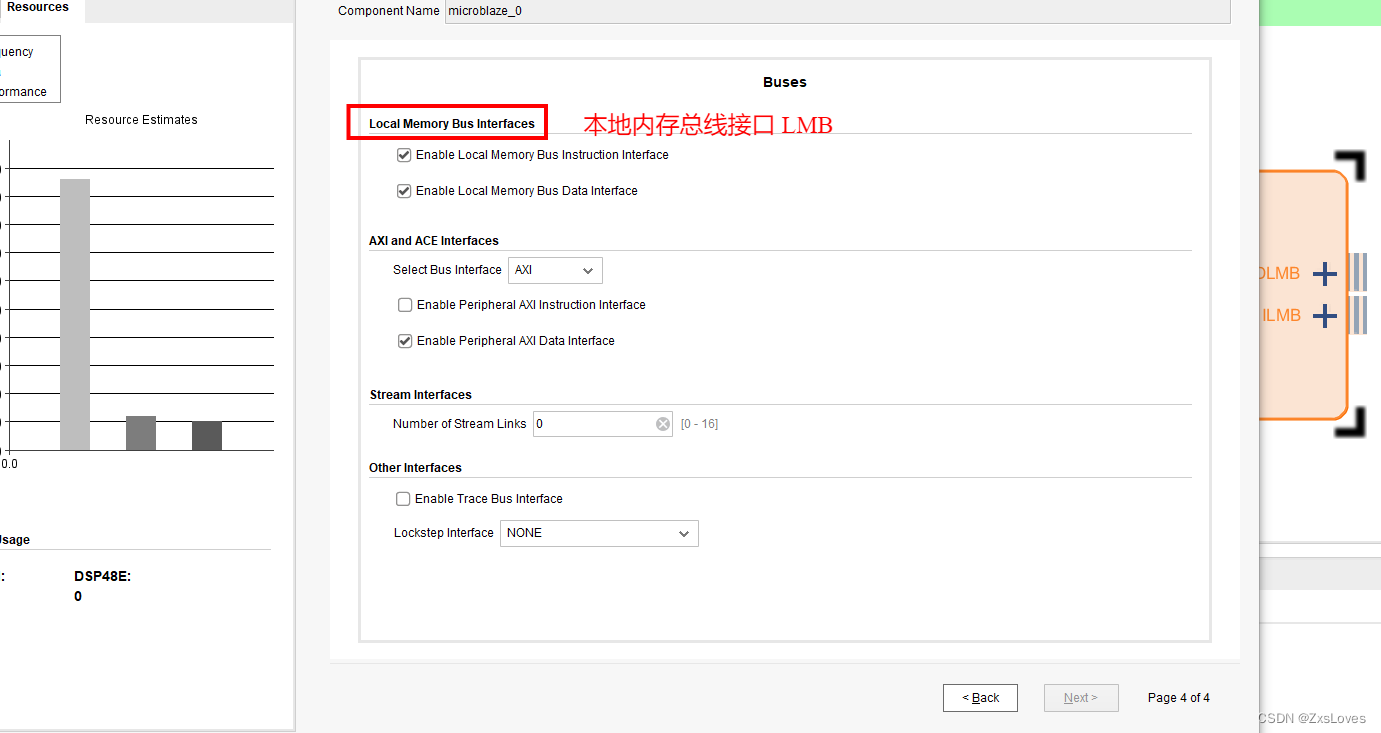

对于 debug 的 调配

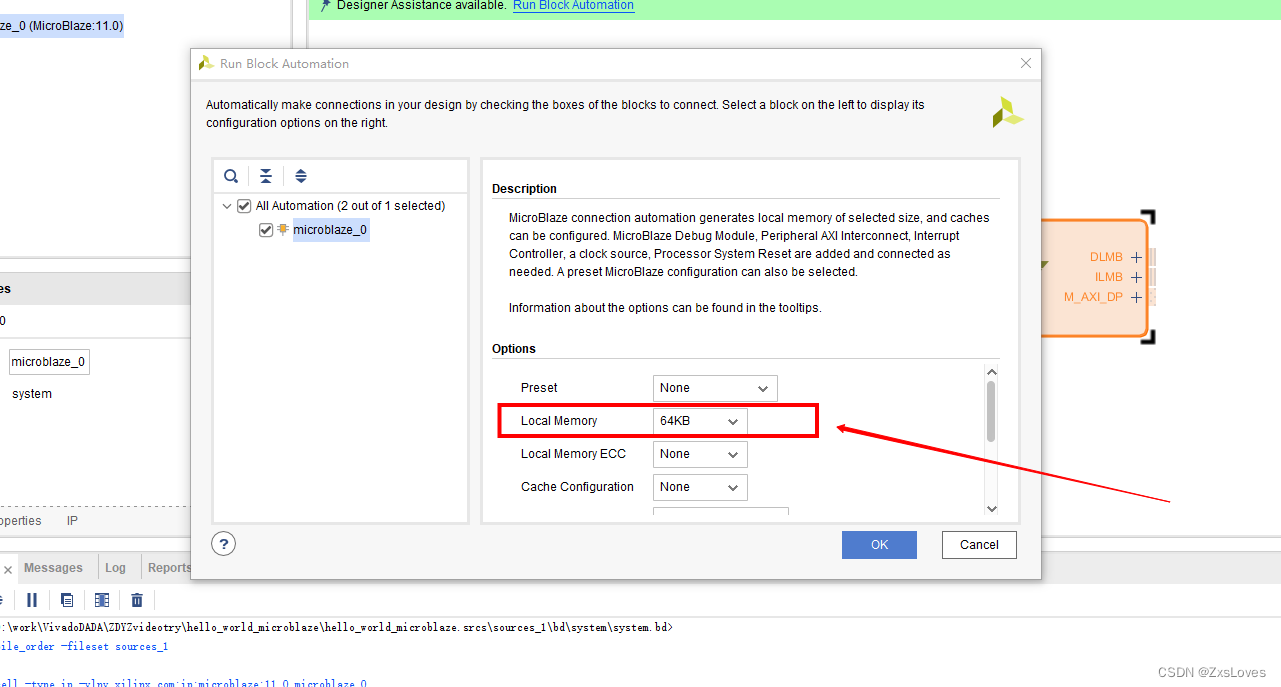

Run Block Automation

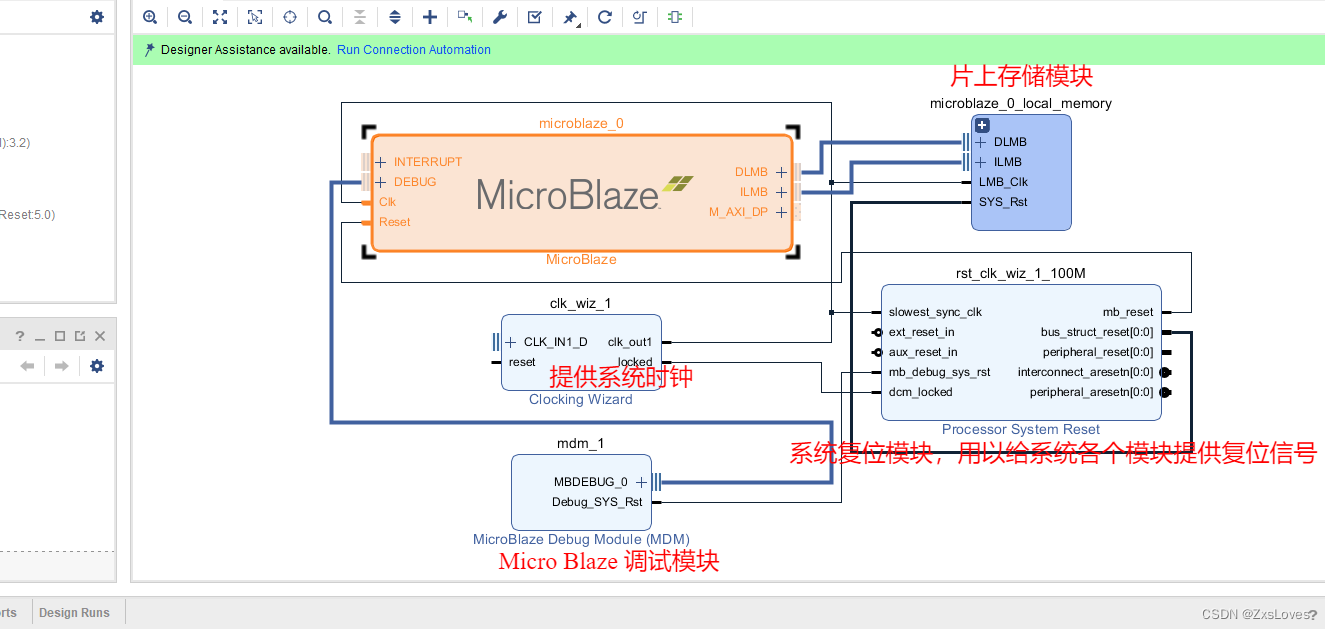

然后点击 OK 接下来会多产生几个不同的Block

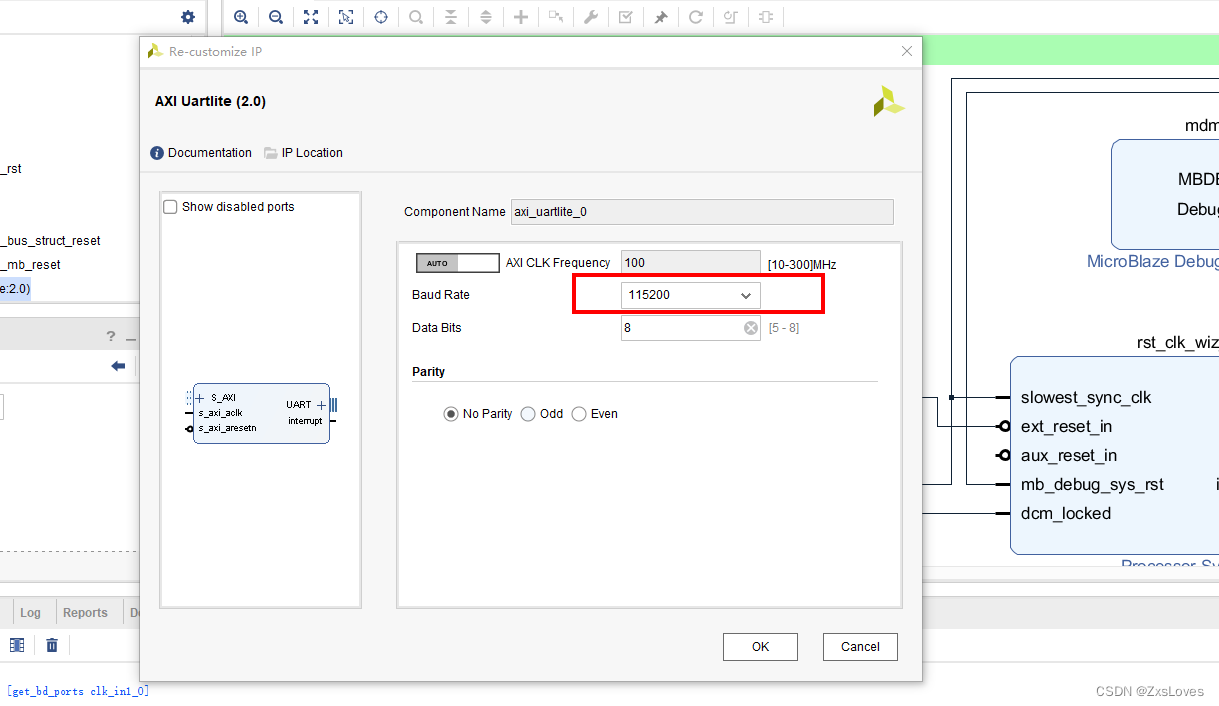

我们现在要用串口打印信息,因此还需添加 Axi Uartlite IP 核

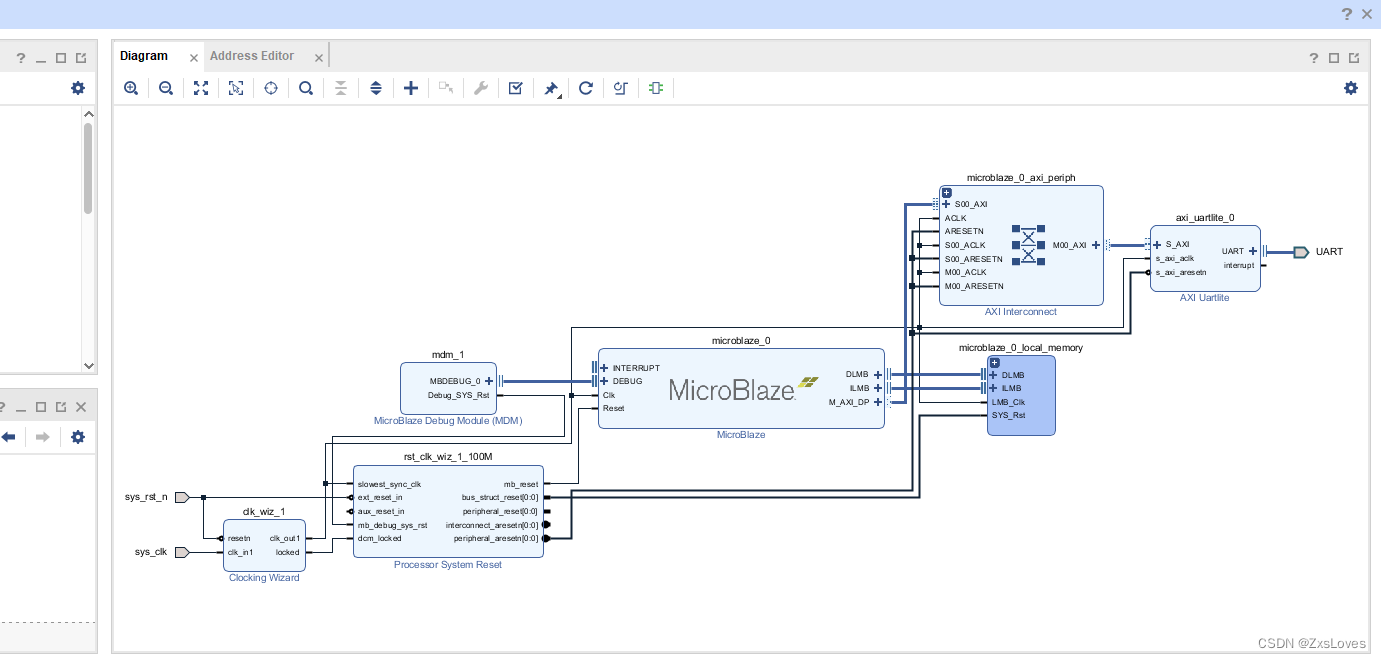

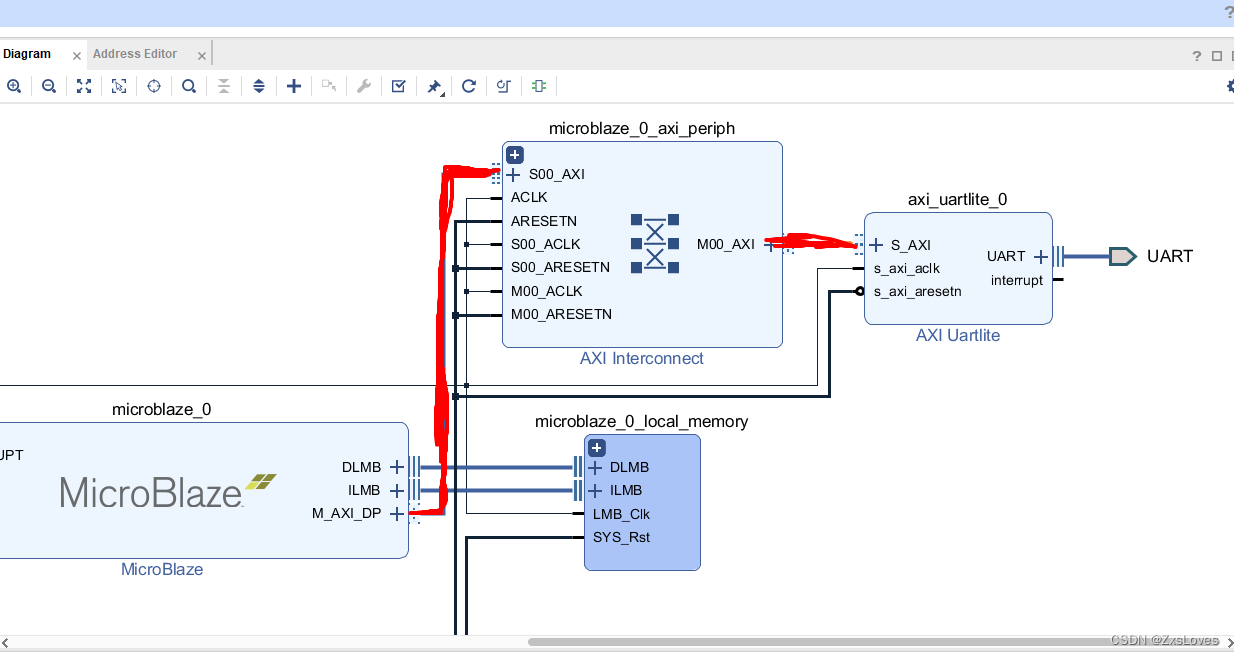

下面是得出的hello world 的 Block Design

在自动连接之后 添加了 AXI Interconnect

我们观察整个系统 会发现 有这样的连接

橙色高亮的两组信号线表明,在这个设计中,AXI 互联实现了由主器件(MicroBlaze)到从器件(AXI Uartlite)一对一的连接。它也可以实现一对多、多对一以及多对多的 AXI 接口连接。本次实验中,AXI Interconnect IP 就实现了 MicroBlaze 与 AXI Uartlite 的互联,MicroBlaze 中产生的数据能够通过 AXI 协议传输到 AXI Uartlite 模块,AXI Uartlite 模块接收的数据也可以通过 AXI 协议传输到MicroBlaze。

一个很大的注意点 :

我们会观察到 为什么在纯 FPGA端 点击之后 我们会需要添加 管脚约束 而在 之前的 zynq 上并没有 很强烈的这种要求

因为 zynq 是 带有 ARM核 的 结构 在底板上 已经把很多 东西接上去 相当于 之前已经配置好了 所以我们并不需要 额外的操作

但是对于软核而言 我们利用了 FPGA的全能性 用内部的机能 构建出了 一个假的但是很正的 CPU 这就是 软核的本质

所以我们 在使用中 我们 需要编排 添加一下 管脚约束

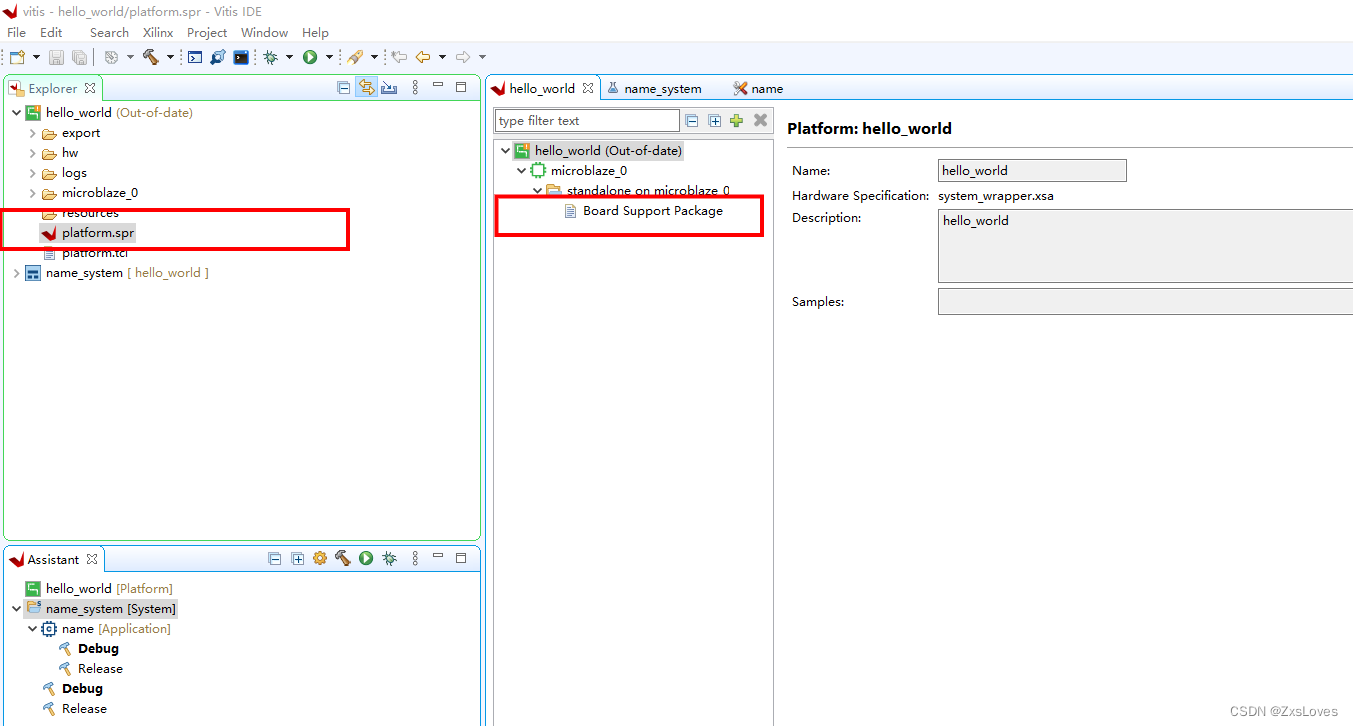

BSP 的 板级验证包在这里

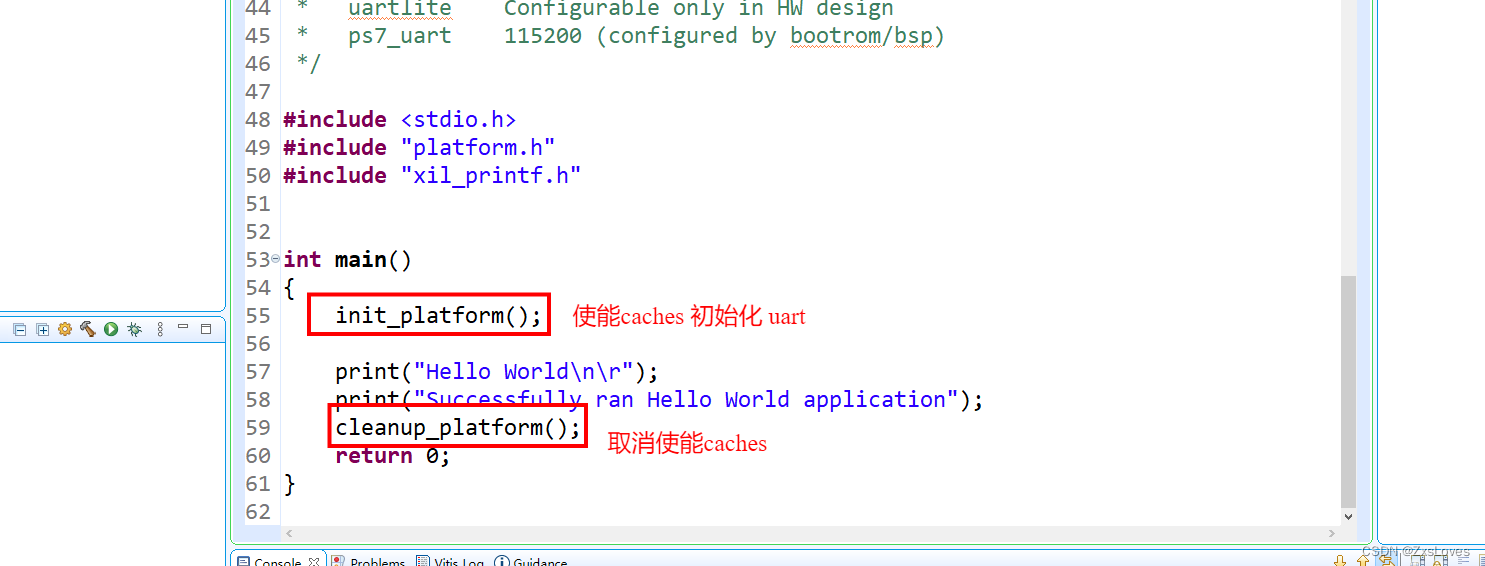

我们点击进入src文件夹 对.c文件进行分析